- 2025-11-24

Wprowadzenie do Verilog: podstawy, składnia, przykłady projektów i materiały edukacyjne dla początkujących

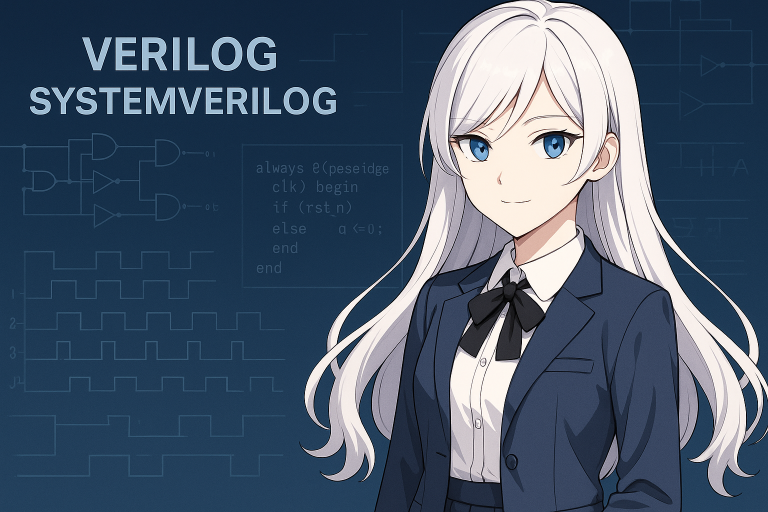

1. Co to jest Verilog? Przegląd i zastosowania Podstawowa definicja Verilog Verilog jest jednym z języków opisu sprzętu (HDL) używanych do projektowania układów cyfrowych. Podczas gdy języki programow […]