- 2025-11-24

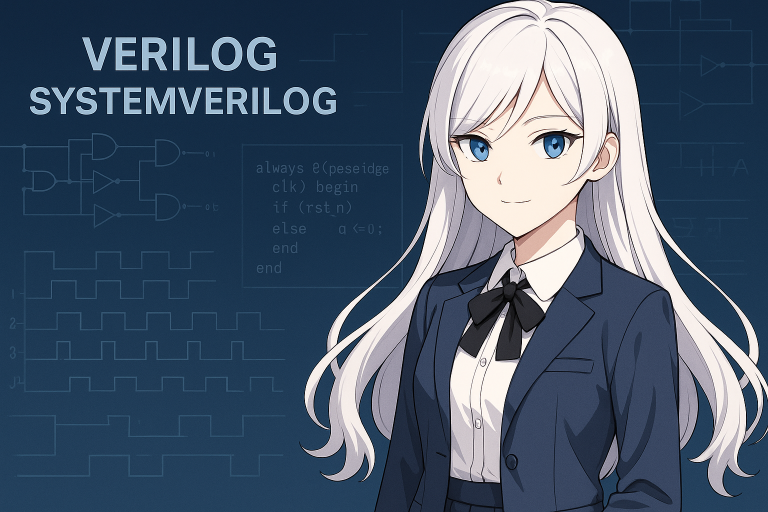

Verilog 소개: 기본, 문법, 설계 예제 및 초보자를 위한 학습 자료

1. Verilog란? 개요와 사용 사례 Verilog의 기본 정의 Verilog는 디지털 회로 설계에 사용되는 하드웨어 기술 언어(HDL) 중 하나입니다. 소프트웨어 프로그래밍 언어가 컴퓨터 프로그램을 기술하는 것과 달리, Verilog는 디지털 회로와 시스템의 동작을 기술하는 데 사용됩니다. 이 언어를 사용하면 복잡한 회로 설계를 단순화하고 시뮬레이션 […]