- 2025-11-24

Introducción a Verilog: conceptos básicos, sintaxis, ejemplos de diseño y recursos de aprendizaje para principiantes

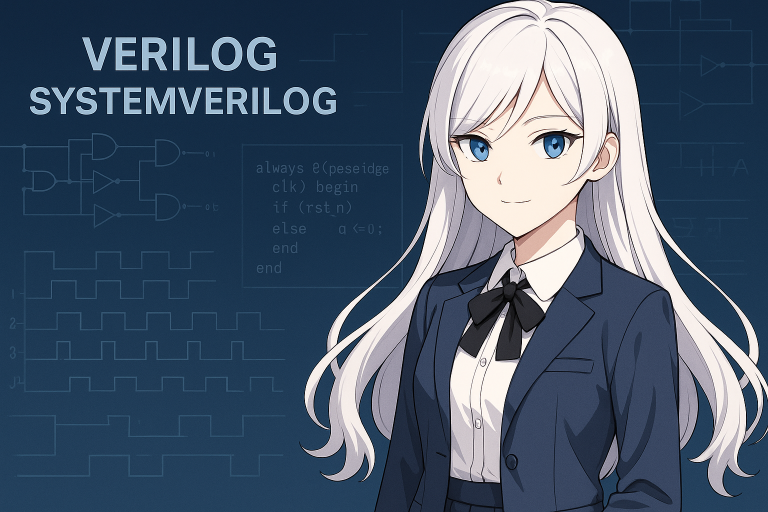

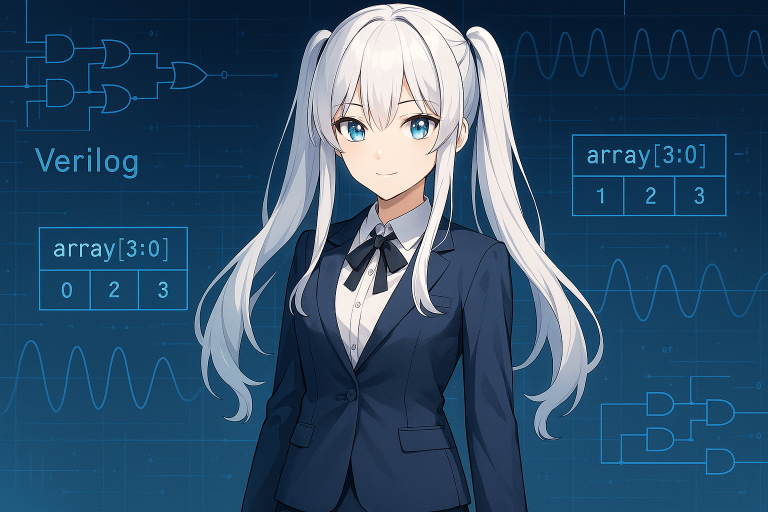

1. ¿Qué es Verilog? Visión general y casos de uso Definición básica de Verilog Verilog es uno de los lenguajes de descripción de hardware (HDL) utilizados para diseñar circuitos digitales. Mientras qu […]