- 1 1. はじめに:なぜVerilogで「force」文が話題になるのか

- 2 2. Verilogにおける「force」文の基本

- 3 3. force文の実践的な使い方・コード例

- 4 4. force文を使うべき場面と、知っておきたいメリット/デメリット

- 5 5. force文を安全かつ効果的に使うための実践Tips(ベストプラクティス)

- 6 6. よくある誤りとトラブルシュート

- 7 7. まとめ:force文の役割と「正しい使い方」を理解する

- 8 8. FAQ(よくある質問)

- 8.1 Q1. force 文は合成できますか?(FPGAやASICで動きますか?)

- 8.2 Q2. force した信号は、release しないとどうなりますか?

- 8.3 Q3. 下位モジュール内部の信号にも force できますか?

- 8.4 Q4. 強制しているのに値が変わらないことがあります。なぜ?

- 8.5 Q5. テストベンチで force を使いすぎると問題ですか?

- 8.6 Q6. 強制した値を一定期間だけ使いたい場合、どう書けば良い?

- 8.7 Q7. 状態機械(State Machine)の特定ステートだけ試したい場合も force できますか?

- 8.8 Q8. force 文と assign 文はどちらが優先されますか?

- 8.9 Q9. force 文を使うと波形上に何か特別なマークはつきますか?

- 8.10 Q10. SystemVerilogにも force はありますか?

- 9 ◆ FAQまとめ

1. はじめに:なぜVerilogで「force」文が話題になるのか

Verilogで回路設計や検証をしていると、あるタイミングから突然タイミングチャートがおかしくなったり、「本当はこういう条件も試したいのに、テストベンチ側の作り込みが追いつかない……」という場面によく出会います。

そんなときに名前が挙がるのが、今回の主役である 「force」文 です。

force文は、一言でいえば 「シミュレーション中に信号の値を強制的に上書きするための仕組み」 です。

通常は回路やテストベンチが信号を駆動しますが、その流れを一時的に奪って「今だけこの値で動いてほしい」と指定できるイメージです。

ここでは、まず初心者の方にも分かりやすいように、背景となる考え方からゆっくり整理していきます。

検証の現場で起きる「ちょっと困った」状況

ハードウェア設計のフローでは、Verilogで回路を書いたあとに、テストベンチを用意してシミュレーションを行い、波形を観察しながら動作が正しいかどうかを確認します。

ところが、実務や学習の現場では次のような悩みがよく出てきます。

- 本番ではあり得るが、普通にテストベンチを書くと再現しづらい状況 を試したい

- 既存のテストベンチを大きく書き換えずに、一部の信号だけ強制的に変えて挙動を見たい

- バグの切り分けのために、特定の信号を一時的に固定した状態で動かしてみたい

例えば、

- 外部から来るはずのリセット信号を、ある時刻だけ無理やり 1 にしてみたい

- 本来は発生しないはずの信号の組み合わせを、あえて作って動かしてみたい

といったケースです。

こうした「例外的な条件」を試すためだけにテストベンチを大幅改修するのは大変ですし、既存の動作に影響を与えてしまうリスクもあります。

そこで登場するのが「force」文

このようなときに便利なのが force文 です。

- ある信号に対して、シミュレータ側から「強制的にこの値で動いて」と指示できる

- もともとの駆動元(always文やassign文など)よりも 強い優先度 で値を上書きできる

- 必要がなくなったら release文 で元の駆動に戻せる

というのが、force文の大まかな役割です。

ポイントは、force文は 「あくまでシミュレーション上の便利テクニック」 であり、実チップやFPGA上で同じようなことができるわけではない、という点です。

あくまで「テストベンチの補助ツール」として使うイメージを持っておくと、誤解が少なくなります。

初心者ほど知っておきたい「force文」の立ち位置

初学者のうちは、

- alwaysやassignで信号を作る

- テストベンチから入力を与える

といった、比較的まっすぐな書き方だけに慣れている方が多いと思います。

しかし実際の検証現場では、

- バグの再現のために、一時的に信号をねじ曲げる

- 設計修正を待たずに、テストベンチ側から条件を差し替える

といった、少し“裏ワザ”的なアプローチが必要になる場面がどうしても出てきます。

force文はまさにそのための仕組みであり、「知っているかどうか」でデバッグ効率が大きく変わってきます。

この記事で学べること

この記事では、次のような流れで Verilogのforce文 を分かりやすく解説していきます。

- force文とは何か、どんな場面で使うものなのか

- 基本的な構文と書き方

- 対になる release文 とセットでの使い方

- テストベンチでの実用的な例

- 便利な一方で、やりすぎると危険になる落とし穴

- 実務で意識しておきたいベストプラクティスや注意点

「force文って危ないと聞いたけど、何がどう危ないの?」という不安も含めて、初心者の方でもイメージを持ちやすいように、具体例を交えながら丁寧に整理していきます。

2. Verilogにおける「force」文の基本

force文を理解するためには、まず 「通常の信号駆動」と「強制的な信号上書き」の違い を押さえておく必要があります。ここでは、構文・役割・通常の信号との優先度など、基礎となる部分を整理します。

force文とは何か

force文とは、Verilogシミュレーション中に 信号へ強制的に値を割り当てるための特殊な構文(ステートメント) です。

通常は以下のように、信号は

assignalwaysブロック- モジュールの入力信号としての駆動

など、コードで定義した「本来の駆動源」によって値が決まります。

しかし、検証の中では、

- 一時的にこの信号の値を固定したい

- 本来の駆動を無視して値を与えたい

- 強制した値で動作を観察したい

といった状況が生じます。

この「本来の駆動よりも優先して値を決める」ための仕組みが force文 です。

基本構文

force文の基本的な書き方はとてもシンプルです。

force <信号名> = <値>;

例:

force clk = 1'b0;

force reset = 1;このように書くと、該当の信号は 本来の駆動ロジックを無視して 指定した値に強制されます。

通常の assign 文や always 文による駆動よりも強い優先度を持つため、たとえ別の always ブロックで値を変えようとしても、強制期間中はその値が変わりません。

release文について(forceとセットで使う)

強制は便利ですが、そのままではずっと値が固定されてしまいます。

そこで使うのが release文 です。

release <信号名>;

これにより、信号は強制状態が解除され、

- assign

- always

- 入力駆動

といった本来の駆動に戻ります。

force と release は 必ずセットで理解 しておくべきペアです。

階層信号にも適用できる

force文はトップ階層の信号だけでなく、下位モジュール内の信号にも適用できます。

force top.u1.internal_sig = 1;これはシミュレーションにおける非常に強力な機能で、モジュール内部の一部だけを操作することも可能になります。

ただし、階層を深く force すると、テストベンチが複雑化しやすいため、後ほど触れるベストプラクティスで注意点を整理します。

force文は合成不可(シミュレーション専用)

ここで最も重要なポイントがあります。

force文は論理合成できません。

つまり、FPGAやASICの回路として実現することはできず、あくまで シミュレーション専用の構文 です。

実機で同じように“強制代入”をすることは不可能なので、「実機では起きない動作をさせてしまう」可能性がある点にも注意が必要です。

force文の性質をまとめると

- シミュレーション中に値を強制的に上書きする

- 本来の駆動よりも圧倒的に強い優先度を持つ

- 必ず release とセットで使い、強制状態を解除する

- 下位モジュールの信号にも適用できる

- 合成不能(シミュレーション専用)

- テストベンチでのデバッグ・検証に特化した構文

という特徴があります。

3. force文の実践的な使い方・コード例

ここでは、実際のシミュレーションで force 文をどのように活用するのかを、具体的なコード例とともに解説します。

初心者でもイメージしやすいように、基本→応用の順番で紹介します。

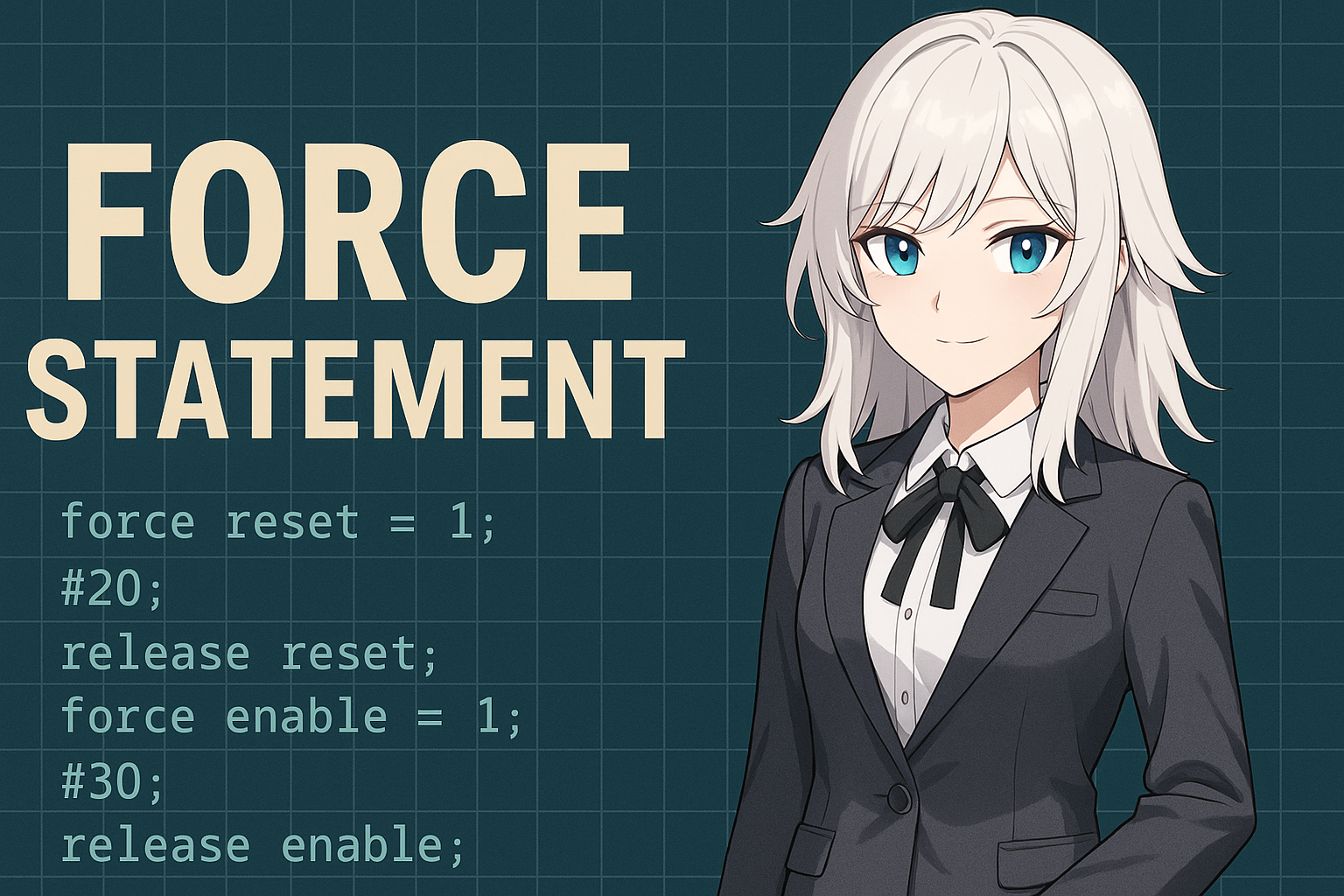

基本的なforce文の例

まずはシンプルな例として、テストベンチから 特定の信号を一時的に上書きする パターンを見てみましょう。

例:リセット信号を強制する

initial begin

// 本来のリセットはテストベンチで制御されているが、

// ここだけ強制的に 1 を与えてみる

force reset = 1;

#20; // 20ns だけ強制

release reset; // 強制解除

endこのコードでは、20ns の間だけ reset を強制的に 1 に固定し、その後 release で元の駆動に戻しています。

ポイント

- 「force → 指定期間だけ待つ → release」の流れは基本中の基本

- 強制期間中は、assign や always による値の変化は無効化される

信号の変化をシミュレーション中に作り出す

force 文は「一定期間だけ値を固定する」だけでなく、指定したタイミングで 強制的に値を変化させる こともできます。

initial begin

#50; // 50ns 後

force clk = 1'b0; // 強制的に0にする

#20;

force clk = 1'b1; // 今度は強制的に1へ

#10;

release clk; // 強制を解除し、もとのクロック生成ロジックへ戻る

endこの例では、本来はテストベンチで生成していた clk に割り込み、任意の瞬間だけクロックを操作しています。

どんな場面で使う?

- 特定のタイミングだけクロックを止めたい

- 故意にクロック周期を乱して挙動を観察したい

- インシデント(異常動作)の再現

force文が「デバッグに強い」と言われる理由がここにあります。

階層パスを使った内部信号のforce

force文の大きな利点のひとつが 「下位モジュールの内部信号にアクセスできる」 ことです。

例:階層パスを用いる

initial begin

force top.u_core.state = 3'b101;

#10;

release top.u_core.state;

end

top モジュール → u_core モジュール → state 信号

という階層構造になっている場合、内部信号であっても強制可能です。

この機能が特に役立つ場面

- 内部ステートマシンの特定状態だけを強制して挙動をチェック

- 本来は外部から制御できない内部信号の「例外状態」を再現

- 設計者と検証者で「切り分け」のために内部信号を操作

ただし、階層指定が深くなるほど可読性が落ちるため、後で紹介する「ベストプラクティス」を参考に慎重に使いましょう。

force文で“異常ケース”を作る例

設計検証では、本来起こってはいけない条件を作って動作確認したい場面もあります。

例:本来同時には立たない2信号をあえて立たせる

initial begin

force req = 1;

force ack = 1; // 普段は req と ack が同時に立つことはない

#15;

release req;

release ack;

endこれにより、

「もし設計上想定外の状態が発生したらどうなるか?」

を確認できます。

実務では、

- バグの切り分け

- セーフティチェック

- 競合状態の再現

などによく使われる方法です。

まとめ:このセクションで学んだこと

- force文は「信号を強制的に上書きする」操作

- クリティカルな場面の再現に非常に有効

- release とペアで使うことが大前提

- 階層パスを使えば内部信号も force 可能

- “異常ケース”を作り、デバッグ・設計見直しに役立つ

4. force文を使うべき場面と、知っておきたいメリット/デメリット

force文は非常に強力なツールですが、「とりあえず使えば便利」というものではありません。

使いどころや注意点を理解しないと、シミュレーション結果の信頼性を損なったり、問題の切り分けが難しくなってしまうこともあります。

ここでは、force文を使うべきケース と 避けるべきケース を明確にしながら、メリット・デメリットを整理します。

force文を使うべき場面

異常系・例外条件の再現(最も代表的な用途)

通常のテストベンチでは再現しづらい「異常状態」を作るときに最適です。

- クロックの乱れや停止を再現したい

- 本来あり得ない信号の組み合わせを故意に発生させたい

- 内部ステートを特定の位置に強制して、例外遷移を確認したい

こういった“例外条件の強制”は、実務のデバッグでも頻出します。

既存のテストベンチを大きく変更せずに検証したいとき

大規模なテストベンチを書き換えるのは時間がかかりますし、誤動作のリスクも増えます。

そこで force 文を使えば、

- テストベンチを最小限の修正で 欲しい条件を実現

- 一部分だけ動作を差し替えて、手早く結果を確認

といった “ピンポイント検証” ができます。

設計者と検証者の「切り分け作業」に便利

例えばバグが起きたとき、

- 本当にその信号が原因なのか?

- 別の信号を固定したら現象がどう変わる?

といった確認をするために、force文は極めて有効です。

1つずつ信号を強制 → 変化を見る

という手法は、実務の検証現場でもよく使われます。

force文のメリット

1. 再現が難しい状況を簡単に作れる

異常系テスト・境界条件テストにおいて、

「普通に動かすと絶対に起きない状況」 を再現できる点は大きな武器です。

2. デバッグの効率が大幅に向上する

内部信号を強制することで、原因箇所を素早く特定できます。

特に階層パスを使った内部ステート強制は、

デバッグの強力な手段になります。

3. テストベンチを壊さずに検証できる

大規模なテスト環境を書き換えるリスクを避け、

必要な信号だけ強制して検証できます。

force文のデメリット

1. 強制状態が複雑化し、原因が追えなくなることがある

force文を多用すると、

「なぜその値になったのか?」が分かりづらくなる

という問題が発生します。

波形上は正しく見えても、実際には force が強制していたせいで、

本来の挙動が確認できていない場合があります。

2. 強制を解除し忘れると予期せぬ挙動になる

releaseを忘れた場合、

- テスト全体が“強制値で動いたまま”になる

- 本来の駆動が有効化されず、結果が不正になる

- 「バグだと思ったら、release忘れだった」という事故が起きる

といった問題が発生します。

3. 実機では再現できない動作になり得る

forceは 合成不可(実機の回路にならない)ため、

- FPGA/ASICでは絶対に起こらない状況

- シミュレーション特有の動作

を発生させてしまう可能性があります。

検証用としては許容できますが、

「forceの結果を前提とした設計判断」 をしてしまうと危険です。

4. 階層パスを使ったforceはテストベンチの依存度を高める

内部信号に直接アクセスするため、

- モジュール名を変更すると動かなくなる

- 階層構造に依存しすぎる

- 可読性が悪くなる

といった欠点もあります。

まとめ:force文は「便利だが慎重に扱うべきツール」

force文は非常に強力ですが、

「異常系再現」「デバッグ」「部分的な検証」 に限定して使うのが賢い方法です。

通常のテストベンチの代わりに多用してしまうと、

シミュレーションの信頼性が下がり、バグを見逃す原因にもなります。

5. force文を安全かつ効果的に使うための実践Tips(ベストプラクティス)

force文は非常に便利ですが、使い方を誤るとシミュレーションの信頼性が落ちたり、デバッグ時間がかえって長引くこともあります。

ここでは、プロの検証エンジニアが実務で意識している “安全で効率の良い使い方” を、初心者にも分かりやすい形でまとめています。

必ず「force → release」のペアで管理する

force文の最も大事な原則は、

強制したら必ず解除する。

ということです。

良い例

force reset = 1;

#20;

release reset;悪い例(releaseがない)

force reset = 1; // ← 強制しっぱなし

release を忘れると、以下のようなトラブルが発生します。

- 以降のテストがすべて「強制された信号」で動く

- 波形が正しく見えても、実際は本来の駆動ロジックが無効化されている

- 結果を間違って解釈してしまう

テストベンチを書く際は、

force と release を必ずセットで書く癖をつける

ことが非常に重要です。

強制させる時間(期間)を必ず明示する

force文でよくある失敗が、

「いつまで強制し続けるのか」 を曖昧にしてしまうこと。

強制値を与えたら、その効果範囲を明確にする必要があります。

悪い例(タイミングが曖昧)

force enable = 1;

良い例

force enable = 1;

#30;

release enable;「何nsだけ強制するのか?」を明示するだけで、波形解析が格段に楽になります。

階層パスのforceは “最後の手段” として使う

内部信号を直接 force できるのは便利ですが、

階層パスの force は可読性が落ちやすく、長期的な維持が大変です。

例えば、

force top.u1.core.state = 3'b101;のような記述は、以下の問題を抱えます。

- モジュール構造を変更すると動かなくなる

- テストベンチが設計の内部構造に強く依存してしまう

- 誰が見ても理解しにくい

特に現場では、

「どうしてこの信号を内部から force しているの?」

「そもそもこの階層パスは今の設計にもう存在しませんよ」

という混乱がしばしば起こります。

対策

- まずは外部インターフェース側の信号で条件を再現できないか検討する

- どうしても必要な場合に限り、階層 force を使う

- コメントで「なぜこの内部信号を強制しているか」を必ず残す

コメントを丁寧に残す(理由が最も重要)

force文は「なぜこの強制が必要なのか」が分からなくなると危険です。

そのため、実務ではコメントを必ず残すルールを推奨します。

例

force reset_n = 0; // 状態遷移の異常ケースを再現するため強制

#15;

release reset_n;単純なコメントでも、将来の自分や別の開発者が理解しやすくなります。

強制状態が波形で“隠れない”ように意識する

force中の信号は、波形エディタ上では通常の値と同じ表示になります。

これは、

- 「本来の駆動なのか」

- 「forceによる強制なのか」

が見分けづらくなるという問題につながります。

対策としては:

- force中の期間を分かりやすくコメントまたはテストログで明示

- 波形上でマーカー(カーソル)を置いておく

- 波形ウィンドウの注釈機能(ツールによる)を活用する

など、後で振り返った時に分かるよう工夫するのが重要です。

“force頼り”にならない検証を心がける

forceはあくまで デバッグ補助ツール であり、

テストベンチや DUT の正常動作確認において、常用すべきものではありません。

forceを使いすぎると、

- 本来の入力条件が正しく作れていない

- テストベンチが未成熟なのに force でごまかしてしまう

- 実機に反映できない挙動を前提にテストが進行してしまう

といった“設計抜け”に繋がります。

まとめ:force文は「ピンポイントで使う道具」

force文は、

- 異常系再現

- 再現しづらい条件の検証

- バグ切り分け

- 一時的な動作停止や強制変更

といった場面では非常に強力です。

一方で、

- 頻繁に使うべきではない

- 常に release が必要

- 階層forceは依存度が高く危険

- デバッグ目的に限るべき

という特徴も押さえておく必要があります。

6. よくある誤りとトラブルシュート

force文は便利な一方で、少し使い方を誤るだけでデバッグが難航したり、結果の信頼性を損なったりすることがあります。

ここでは、初心者〜中級者が陥りやすい典型的な誤りと、その原因・解決策を具体的に整理します。

強制解除(release)の書き忘れ

もっとも多いトラブルが release を忘れる ケースです。

発生しがちな状況

initial begin

force start = 1;

#20;

// release がないままシミュレーション終了まで進んでしまう

end起きる問題

- 強制状態がずっと継続する

- 本来の駆動ロジックが無視される

- 波形は一見正しく見えても、デバッグ結果が誤ってしまう

解決策

- force と release を同じブロック内に必ずセットで書く

- release を複数回呼んでも問題はないため、「保険として」入れるのもOK

- テンプレート化してしまうのも有効

force sig = value;

#delay;

release sig;階層パスの間違い(よくあるケアレスミス)

内部信号に force する場合、階層パスを間違えると force が効いていないのに効いていると勘違いする 状態になります。

例(間違い)

force top.u1.core.stat = 3'b100;

// 本当は "state" なのに、"stat" と誤記問題点

- エラーが出ないシミュレータもある

- “強制できている”と思い込んでデバッグが迷走する

- 波形を見ても本当の原因に気づけない

対策

- 階層パスを自動補完できる環境(SimVision・Verdiなど)を活用

- テストベンチで

displayを使い、強制が効いたかチェックする - 極力階層forceを避ける(前のセクションのベストプラクティスを参照)

強制中に別の駆動源も値を変えようとして競合する

force 中は本来の駆動を無視しますが、

駆動源が複数ある場合、X(不定値) が発生することがあります。

例

assign a = cond ? 1 : 0; // 通常の駆動

force a = 1'b0; // 強制的に0ケースによっては:

- シミュレータが「force優先」と解釈

- 別のドライバが同時に無理に駆動し → Xになる

など、ツール依存の挙動が出ることもあります。

対策

- force 期間中に他の always / assign が

aを駆動していないか確認 - 必要があれば “disable” やテストベンチ側の駆動 OFF を併用

- 波形で「駆動元」を表示して確認する(ツールのDriverトレース機能)

実装コード(DUT)の修正後に force が影響し続ける

force文は設計内部に依存するため、設計変更後に予期せぬ問題が起きます。

起きがちなケース

- 階層名が変わる

- 内部信号名が変わる

- ステート数が変更された

これにより、force が効かなくなったり、誤った信号を強制してしまうことがあります。

対策

- force 文と release 文をすぐ見つけられるよう、テストベンチを整理しておく

- 設計変更があったら、force の階層を必ず再チェック

- コメントに「依存している階層」を明記する

force に頼りすぎてテストベンチが正しく書けていない問題

force文を多用し過ぎると、

本来のテストベンチ設計が甘くなる

という根本的な問題も発生します。

起こる問題

- テストベンチが正しい入力条件を生成できていないのに、forceでごまかしてしまう

- 強制状態ばかり使うため、通常のフローでの動作確認が不足する

- 実機の動作に繋がる“本来の検証”が手薄になる

対策

- force は「デバッグ」「異常系」「切り分け」に限定

- 通常のテストは force なし を基本とする

- 異常系テストだけ force を使うスタイルに統一する

“強制しているのに値が変わらない” トラブル

force の基本動作を理解していても、

強制した値が反映されない という問題が起こる場合があります。

原因として多いのは:

- 信号が tri-state や wire で、複数ドライバを持つ

- 力関係(drive strength)の設定が影響

- シミュレータ固有のforce挙動

- force が別のブロックで上書きされている

対策

- 該当信号の drive strength を確認

- シミュレータの “driver trace” 機能で駆動元を調べる

- テストベンチ内に同じ信号を force している箇所がないか確認

- モジュール境界を超える駆動をチェック

セクションまとめ

force文で起こるトラブルは、

ほとんどが “書き忘れ・誤記・想定外の競合” から発生します。

このセクションで紹介したように、

- release忘れ

- 階層パスの間違い

- 駆動競合

- 設計変更に伴う force の崩壊

- force過多によるテストベンチの劣化

などを回避することで、force文を安全・確実に扱えるようになります。

7. まとめ:force文の役割と「正しい使い方」を理解する

Verilog の force 文は、テストベンチやシミュレーションにおいて非常に強力なツールです。

しかし、その強さゆえに「使いどころを誤ると危険」でもあります。

このセクションでは、これまで解説してきた内容を整理し、実務や学習で活かすための総まとめを行います。

force文の本質:信号を“強制的に上書きする”ための仕組み

force文は、通常の assign・always・入力駆動を無視し、

「今この信号にはこの値を使ってほしい」

という状況をシミュレータに指示するものです。

そのため、

- 異常系の再現

- バグの切り分け

- 特定条件のテスト

- 設計内部の状態チェック

- テストベンチを大きく変えずに追加検証する手段

といった場面で大きな力を発揮します。

強力だが“常用すべきではない”理由

force文は便利ですが、以下の点に注意が必要です。

- 実機では同じ動作ができない(合成不可)

- 強制状態が続くと元の設計挙動が確認できない

- release忘れが重大なトラブルにつながる

- 多用するとテストベンチが正しく書けなくなる

- 階層パス force による依存が危険

つまり、

「必要な時だけ、ピンポイントで使う」

ことが極めて重要です。

安全な使い方のポイント(要点を再整理)

- force → release は必ずセットで書く

- 時間を明示し、解除忘れを防ぐ

- 強制が必要な理由をコメントする

- 後で読み返した時に混乱を避ける

- 階層パスの force は慎重に

- 可読性と保守性が落ちるため、最後の手段

- 異常系・例外条件の検証に限定する

- 通常テストでは使わない方が健全

- 波形上で force のタイミングが見えるよう工夫する

- デバッグ効率が大幅に改善する

force文は「検証の幅を広げる」ための強力な道具

正しい使い方を理解していれば、force文は検証工程で非常に強い味方になります。

- バグ原因の切り分け

- 想定外条件の再現

- 状態機械の特定ステートを強制して解析

- クロックやリセットなど重要信号の“例外的な操作”

- テストベンチ修正の最小化

といった用途において、forceは一般的な検証技術として活用されます。

逆に使い方が雑だと、

- テスト結果が信用できない

- 想定外の動作の原因に気づけない

- デバッグ工数が増える

といったリスクも伴います。

この記事を通して学べること

本記事では、以下のポイントを体系的に解説してきました。

- force文の基本構文と動作

- release文とのセット運用

- 実践コード例と活用シーン

- メリット・デメリット

- 実務で役立つベストプラクティス

- よくあるトラブルとその対処法

これらを理解しておけば、force文を “危険な裏技” ではなく、使いどころを理解した高度な検証ツール として活用できます。

8. FAQ(よくある質問)

Verilog の force 文は、学習段階でも実務でもよく登場する一方、「思った通りに動かない」「どこまで使っていいのか分からない」といった疑問が多く寄せられるテーマです。

ここでは、初心者から中級者の方までが特に気になりやすいポイントを Q&A形式 でまとめました。

Q1. force 文は合成できますか?(FPGAやASICで動きますか?)

A. いいえ。forceは“シミュレーション専用”であり、論理合成はできません。

force文はシミュレータ上の特殊な機能であって、実際のハードウェア回路には存在しません。

そのため、実機動作の確認には force を使ったテスト結果をそのまま当てはめないよう注意してください。

Q2. force した信号は、release しないとどうなりますか?

A. 強制状態が継続し、本来の駆動ロジックが無効になります。

release を行わない限り、その信号はずっと「強制された値」で動き続けます。

これは波形上では気づきにくく、誤ったデバッグにつながりやすい典型的なミスです。

Q3. 下位モジュール内部の信号にも force できますか?

A. 可能です。階層パス(hierarchical path)を使えば内部信号にもアクセスできます。

force top.u_core.state = 3'b101;

ただし、設計構造に依存するため、階層forceは保守性が低く、乱用は危険です。

基本は外部インターフェースで制御し、それが難しいケースだけに限定しましょう。

Q4. 強制しているのに値が変わらないことがあります。なぜ?

A. 複数のドライバがある、強度設定(drive strength)、シミュレータ固有仕様などが原因です。

よくある原因は:

- tri-state や wire で複数の駆動源が存在する

- force より強いドライバ設定

- 別の force が同じ信号にかかっている

- 階層パスの誤記

- シミュレーションツールが特定の優先順位で解釈している

波形ツールの「Driver Trace」「Force Manager」を使うと原因を特定しやすくなります。

Q5. テストベンチで force を使いすぎると問題ですか?

A. はい。force 一辺倒になると“本来の入力条件を与えるテスト”が不足します。

force はあくまで、

- 異常系再現

- デバッグ

- 条件の切り分け

といった限定的な用途に留め、

通常の動作確認では force を使わずにテストを書きましょう。

force 頼りのテストは、実機の挙動を十分に担保できないため危険です。

Q6. 強制した値を一定期間だけ使いたい場合、どう書けば良い?

A.「force → #遅延 → release」の流れで書きます。

例:

force enable = 1;

#20;

release enable;この形式が最も安全で、強制期間が明確になります。

Q7. 状態機械(State Machine)の特定ステートだけ試したい場合も force できますか?

A. できます。内部信号であれば階層forceが有効です。

ただし、前述のとおり保守性が落ちるため、

コメントやログを残し、設計変更時に破綻しないよう管理しましょう。

Q8. force 文と assign 文はどちらが優先されますか?

A. force 文です。assign や always を含む通常の駆動よりも高い優先度を持ちます。

そのため、force 中は他のブロックが値を書き換えようとしても上書きされません。

Q9. force 文を使うと波形上に何か特別なマークはつきますか?

A. シミュレータによっては“Force中”のマークを付けられますが、標準では付かないことも多いです。

そのため、

- コメント

- ログ出力

- 波形ビューア側の注釈機能

などで「force のタイミング」を分かりやすくしておくことを推奨します。

Q10. SystemVerilogにも force はありますか?

A. はい、基本的に Verilog と同じように使用できます。

ただし、SystemVerilog ではより高度な検証手法(UVMなど)が一般化しているため、

force の利用頻度は環境によって減る傾向があります。

◆ FAQまとめ

- force は「強制上書き」機能であり、合成不可

- release しないと強制が継続

- 階層forceは強力だが慎重に

- 多用は危険。異常系・切り分けなど限定的に使用

- 優先度は通常駆動より高い

- 動かない場合はドライバや階層誤りを疑う