- 2025-11-27

แนะนำ Verilog: พื้นฐาน, ไวยากรณ์, ตัวอย่างการออกแบบ, และแหล่งเรียนรู้สำหรับผู้เริ่มต้น

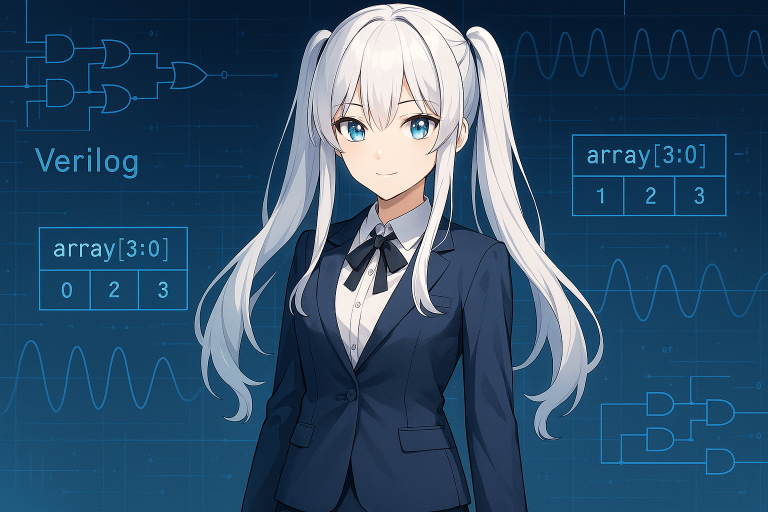

1. Verilog คืออะไร? ภาพรวมและกรณีการใช้งาน คำจำกัดความพื้นฐานของ Verilog Verilog เป็นหนึ่งในภาษาการอธิบายฮาร์ดแวร์ (HDL) ที่ใช้ในการออกแบบวงจรดิจิทัล ขณะที่ภาษาการเขียนโปรแกรมซอฟต์แวร์อธิบายโปรแกรมคอม […]