- 2025-11-24

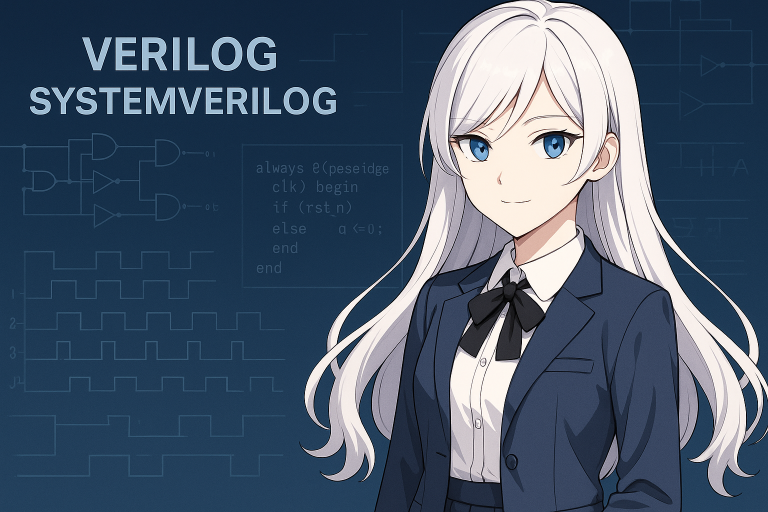

Verilog केस स्टेटमेंट में महारत: सिंटैक्स, उदाहरण, और डिजिटल डिज़ाइन के लिए सर्वोत्तम प्रथाएँ

1. परिचय: Verilog में case स्टेटमेंट का महत्व Verilog HDL (हार्डवेयर विवरण भाषा) डिजिटल सर्किट डिज़ाइन में व्यापक रूप से उपयोग की जाने वाली भाषा है। इसकी विशेषताओं में, case स्टेटमेंट को जटिल शर्तीय श […]